**Data Sheet**

Mar 2006

#### **Features**

- Performs ASK (amplitude shift keyed) modulation and demodulation

- 32 kHz carrier frequency

- Up to 2 kbit/s full duplex data transfer rate

- · On-chip oscillator

- · On-chip tone caller for alerting functions

- · Adjustable tone caller frequencies

- Selectable self-loop test mode

- 5V/2.5mA power supply

- ISO<sup>2</sup>-CMOS and switched capacitor technologies

- 18 Pin DIP

#### **Applications**

- Simultaneous data and voice communication in PABXs

- 2 kbit/s data modem

- "Smart" telephone sets

#### **Ordering Information**

| MT8840AE<br>MT8840AS<br>MT8840ASR<br>MT8840AE1<br>MT8840ASR1 | 18 Pin PDIP<br>18 Pin SOIC<br>18 Pin SOIC<br>18 Pin PDIP*<br>18 Pin SOIC* | Tubes<br>Tubes<br>Tape & Reel<br>Tubes<br>Tape & Reel |  |  |  |  |

|--------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|

| * Pb Free Matte Tin                                          |                                                                           |                                                       |  |  |  |  |

| 0°C to +85°C                                                 |                                                                           |                                                       |  |  |  |  |

#### **Description**

The MT8840 is a carrier over voice modem which allows simultaneous transfer of voice and data over a single pair of wires. Data is transferred on an amplitude shift keyed (ASK) 32 kHz carrier. On-chip filters remove voice frequency signals from the received composite voice and data signal prior to demodulation. The modulating signal is a bit stream with a typical data rate of 2 kbit/s. In addition, the device contains a two tone warbler which functions as a telephone ringer. The device is fabricated in Zarlink's double-poly ISO<sup>2</sup>-CMOS technology utilizing switched-capacitor techniques.

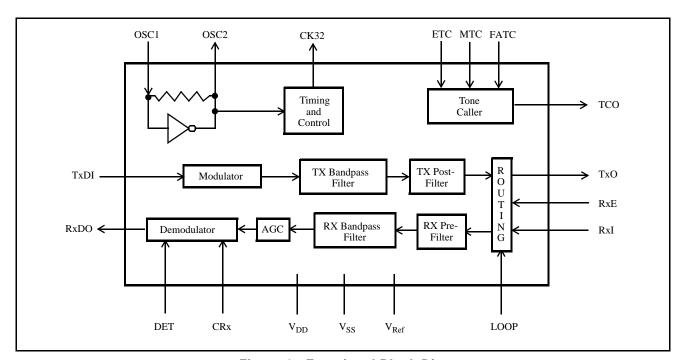

Figure 1 - Functional Block Diagram

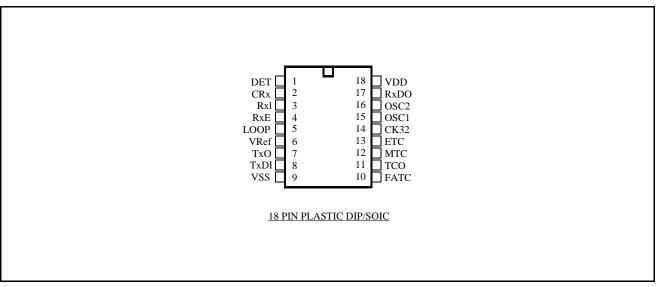

Figure 2 - Pin Connections

### **Pin Description**

| Pin # | Name              | Description                                                                                                                                                                    |                                                                          |  |  |  |  |

|-------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--|--|--|--|

| 1     | DET               | Demodulator detection level adjust input (Analog). Internal resistor divider applies 2.36 V in open circuit condition. Connection of external resistor will vary detect level. |                                                                          |  |  |  |  |

| 2     | CRx               | External AGC time constant adjust input (Ana                                                                                                                                   | log). Connect external capacitor to V <sub>SS</sub> .                    |  |  |  |  |

| 3     | RxI               | Modulated receive signal input (Analog). Bias                                                                                                                                  | sed at V <sub>Ref</sub> .                                                |  |  |  |  |

| 4     | RxE               | Receive enable input (Digital) with internal pu                                                                                                                                | ıll up. Active high.                                                     |  |  |  |  |

| 5     | LOOP              | Self-test mode select input (Digital) with inter-                                                                                                                              | nal pull down. Active high.                                              |  |  |  |  |

| 6     | V <sub>Ref</sub>  | Internal reference supply voltage input (Analog) .                                                                                                                             |                                                                          |  |  |  |  |

| 7     | TxO               | Modulated transmit carrier output (Analog).                                                                                                                                    |                                                                          |  |  |  |  |

| 8     | TxDI              | Transmit data input (Digital).                                                                                                                                                 |                                                                          |  |  |  |  |

| 9     | $V_{SS}$          | Negative power supply.                                                                                                                                                         |                                                                          |  |  |  |  |

| 10    | FATC              | Tone caller center frequency adjust input (Ana                                                                                                                                 | Tone caller center frequency adjust input (Analog).                      |  |  |  |  |

| 11    | TCO               | Tone caller output (Digital).                                                                                                                                                  |                                                                          |  |  |  |  |

| 12    | MTC               | Mute tone caller input (Digital) with internal p                                                                                                                               | oull down. Active high.                                                  |  |  |  |  |

| 13    | ETC               | Enable tone caller input (Digital) with internal                                                                                                                               | Enable tone caller input (Digital) with internal pull down. Active high. |  |  |  |  |

| 14    | CK32              | 32 kHz data strobe output (Digital).                                                                                                                                           |                                                                          |  |  |  |  |

| 15    | OSC1              | Clock Input                                                                                                                                                                    | 3.579545 MHz crystal connected between these                             |  |  |  |  |

| 16    | OSC2              | Clock Output to drive external devices.                                                                                                                                        | pins completes internal oscillator.                                      |  |  |  |  |

| 17    | RxDO              | Receive data output (Digital). Synchronized to CK32.                                                                                                                           |                                                                          |  |  |  |  |

| 18    | $V_{\mathrm{DD}}$ | Positive power supply.                                                                                                                                                         |                                                                          |  |  |  |  |

#### **Functional Description**

The MT8840 contains the modulator and demodulator circuitry for 32 kHz ASK signalling as well as a two-tone warbler (tone caller) to replace the function of the mechanical telephone ringer.

A 32 kHz carrier is 100% amplitude modulated by the digital bit stream applied to input TxDI. This results in an amplitude shift keyed (ASK) 32 kHz carrier. A logical high at TxDI disables the carrier and a logical low enables it. The digitally modulated waveform is shaped by the Tx BANDPASS FILTER and smoothed by the Tx POST FILTER. The signal then enters the routing block where it is transferred to the TxO output.

The modulated 32 kHz receive signal is applied to RxI. With a logical low applied to LOOP and a logical high applied to RxE, receive signals are routed to the Rx PREFILTER. High frequencies are removed by the Rx PREFILTER to prevent aliasing in the switched capacitor Rx BANDPASS FILTER. Voice signals are removed by the bandpass filter which is followed by an AGC circuit. This provides a dynamic range of 20 dB for the receiver. An external 1  $\mu$ F capacitor connected from CRx to V<sub>SS</sub> is required to control the AGC attack and decay time constants. Data is recovered from the received signal in the demodulator. The minimum voltage level to which the demodulator responds may be adjusted by connecting a resistor from DET to V<sub>DD</sub> or V<sub>Ref</sub>. Since DET is the input to a comparator, noise should be kept to a minimum at this pin. The recovered receive data is synchronized to the leading edge of the 32 kHz clock (available at CK32) before appearing at RxDO.

When in loop around mode, the Rx PREFILTER input is internally disconnected from the RxI input pin and connected to TxO. The transmitter output is still available at TxO.

A two tone warbling audio signal is available at TCO when the tone caller enable input (ETC) is high. TCO is internally clamped to  $V_{Ref}$  when the tone caller is disabled. The tone output can be attenuated by 20 dB if a logical high is applied to the tone caller mute input (MTC).

#### **Applications**

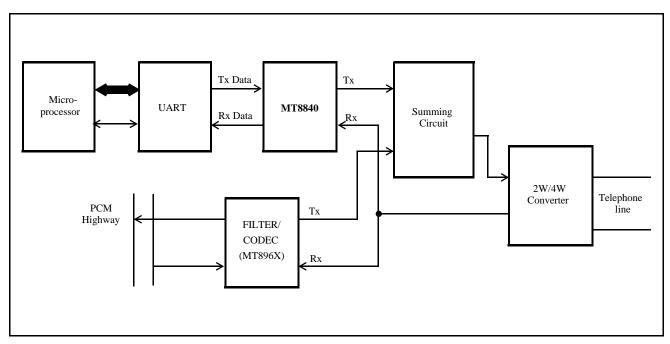

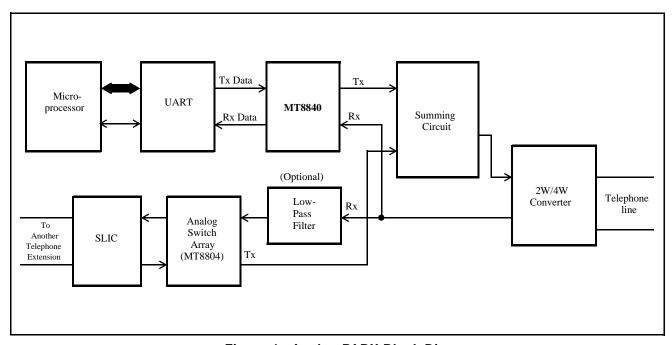

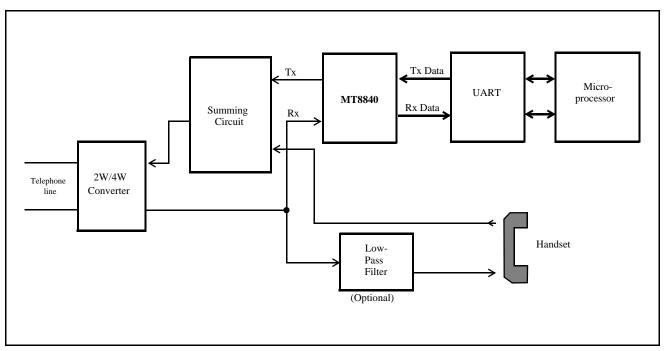

Figures 3 through 5 show how the MT8840 may be utilized to transfer data and voice simultaneously over a single pair of wires in digital or analog PABXs and "smart" telephone sets. In all three figures a microprocessor sends/receives data to/from the MT8840 via a UART which converts the data format from parallel-to-serial or serial-to-parallel for the transmit and receive directions, respectively. In the receive direction the MT8840 has on-board filters to reject voice-band signals leaving only the 32 kHz carrier. This carrier is then demodulated to recover the received data. In the transmit direction the data to be sent is modulated and passed on to a summing circuit which sums the modulated 32 kHz carrier and voiceband signals for transmission over the telephone line. In the PABX the Filter/Codec has filters which reject the 32 kHz carrier from the received composite voice and data signal allowing only voiceband signals to pass through which are then PCM encoded for digital switching. However, in both the analog PABX and smart telephone set, lowpass filters could be included to bandlimit the received signal leaving only voice signals to be passed on to the switch array or handset earpiece.

Figure 3 - Digital PABX Block Diagram

Figure 4 - Analog PABX Block Diagram

Figure 5 - Smart Telephone Set Block Diagram

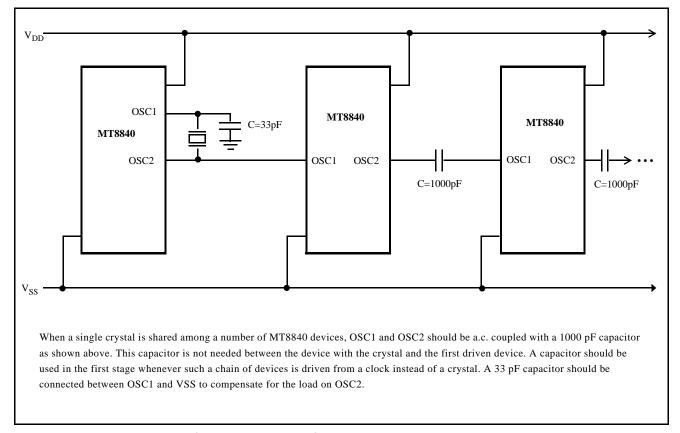

Figure 6 - Crystal Oscillator Connections for Driving Multiple MT8840s

## **Absolute Maximum Ratings\***

|   | Parameter                 | Symbol                                | Min.                 | Max.                 | Unit |

|---|---------------------------|---------------------------------------|----------------------|----------------------|------|

| 1 | Supply Voltage            | $V_{\mathrm{DD}}$ - $V_{\mathrm{SS}}$ | -0.3                 | +7.0                 | V    |

| 2 | Voltage On Any Pin        | V <sub>Max</sub>                      | V <sub>SS</sub> -0.3 | V <sub>DD</sub> +0.3 | V    |

| 3 | Current On Any Pin        | I <sub>Max</sub>                      |                      | 20                   | mA   |

| 4 | Storage Temperature       | $T_{S}$                               | -65                  | +150                 | °C   |

| 5 | Package Power Dissipation | P <sub>Diss</sub>                     |                      | 850                  | mW   |

<sup>\*</sup> Exceeding these ratings may cause permanent damage. Functional operation under these conditions is not implied.

### **Recommended Operating Conditions**

|   | Parameter                 | Symbol            | Min. | Тур.                 | Max. | Unit |

|---|---------------------------|-------------------|------|----------------------|------|------|

| 1 | Operating Supply Voltages | $V_{\mathrm{DD}}$ | 4.75 | 5                    | 5.25 | V    |

| 2 |                           | V <sub>Ref</sub>  |      | $0.4V_{\mathrm{DD}}$ |      | V    |

| 3 | Operating Supply Currents | $I_{DD}$          |      | 2.5                  | 5.0  | mA   |

| 4 |                           | I <sub>Ref</sub>  |      |                      | 200  | μΑ   |

| 5 | Operating Temperature     | T <sub>O</sub>    | 0    |                      | +85  | °C   |

| 6 | Load Capacitance (TxO)    | $C_{L}$           |      |                      | 50   | pF   |

| 7 | Load Resistance (TxO)     | $R_{L}$           | 10   |                      |      | ΚΩ   |

|    |        | Characteristics                | Sym.            | Min. | Тур. | Max. | Unit | Test Conditions          |

|----|--------|--------------------------------|-----------------|------|------|------|------|--------------------------|

| 1  |        | Input Current                  | I <sub>IN</sub> |      |      | ±10  | μΑ   | $V_{IN} = 0$ to $V_{DD}$ |

| 2  | D<br>I | Input Low Voltage              | V <sub>IL</sub> | 0    |      | 1.5  | V    |                          |

| 3  | G      | Input High Voltage             | V <sub>IH</sub> | 3.5  |      | 5.0  | V    |                          |

| 4  | I      | Output Low Voltage             | V <sub>OL</sub> |      |      | 0.4  | V    | $I_{OL} = 0.4 \text{mA}$ |

| 5  | T<br>A | Output High Voltage            | V <sub>OH</sub> | 4.6  |      |      | V    | $I_{OH} = 0.4 \text{mA}$ |

| 6  | L      | Output Drive Current           |                 |      |      |      |      |                          |

| 7  | _      | N Channel Sink (Except OSC2)   | I <sub>OL</sub> | 0.4  |      |      | mA   | $V_{OL} = 0.4V$          |

| 8  | I /    | OSC2                           |                 | 0.1  |      |      | mA   |                          |

| 9  | Ó      | P Channel Source (Except OSC2) | I <sub>OH</sub> | 0.4  |      |      | mA   | $V_{OH} = 4.6V$          |

| 10 |        | OSC2                           |                 | 0.1  |      |      | mA   |                          |

| 11 |        | Input Current (RxI, FATC)      | I <sub>IN</sub> |      |      | ±10  | μΑ   | $V_{IN} = 0$ to 5.0V     |

| 12 |        | Input Resistance (FATC)        | R <sub>IN</sub> | 500  |      |      | ΚΩ   |                          |

| 13 | A      | (DET to V <sub>DD</sub> )      |                 |      | 170  |      | ΚΩ   |                          |

| 14 | N      | (DET to V <sub>Ref</sub> )     |                 |      | 23   |      | ΚΩ   |                          |

| 15 | A<br>L | Input Capacitance (RxI)        | C <sub>IN</sub> |      | 50   |      | pF   |                          |

| 16 | Ö      | (FATC)                         |                 |      | 10   |      | pF   |                          |

| 17 | G      | Any Digital Input              |                 |      | 5.0  | 7.5  | pF   |                          |

| 18 | I      | Output Resistance (TxO)        | R <sub>O</sub>  |      | 100  |      | Ω    |                          |

| 19 | /      | (TCO)                          |                 |      | 3    |      | ΚΩ   | MTC = 0                  |

| 20 | О      | (TCO)                          |                 |      | 30   |      | ΚΩ   | MTC = 1                  |

| 21 |        | Output Offset Voltage (TxO)    | V <sub>O</sub>  |      | ±25  | ±200 | mV   |                          |

| 22 |        | Output Voltage (DET)           | V <sub>O</sub>  | 2.20 | 2.36 | 2.55 | V    | See Note 1               |

Notes: 1. Voltage specified is generated internally and measured with no external components connected to DET

**A.C. Characteristics -**  $V_{DD}$ =5.0 $V\pm5\%~V_{SS}$ =0V~T=0 - 85 $^{\circ}$ C (All voltages are referenced to  $V_{SS}$ /GND)

|    |          | Characteristics               | Sym.                | Min.   | Тур.              | Max.   | Unit      | Test Conditions                                   |

|----|----------|-------------------------------|---------------------|--------|-------------------|--------|-----------|---------------------------------------------------|

| 1  |          | Crystal/Clock Frequency       | $f_{C}$             | 3.5759 | 3.5795            | 3.5831 | MHz       | OSC1, OSC2                                        |

| 2  |          | Clock Input (OSC 1)           |                     |        |                   |        |           |                                                   |

| 3  |          | Rise Time                     | t <sub>LHCI</sub>   |        |                   | 100    | ns        | 10% - 90% of (V <sub>DD</sub> - V <sub>SS</sub> ) |

| 4  | D        | Fall Time                     | t <sub>HLCI</sub>   |        |                   | 100    | ns        |                                                   |

| 5  | I        | Duty Cycle                    | $DC_{CI}$           | 40     | 50                | 60     | %         |                                                   |

| 6  | G<br>I   | Clock Output (OSC 2)          |                     |        |                   |        |           |                                                   |

| 7  | T        | Rise Time                     | t <sub>LHCO</sub>   |        | 100               |        | ns        | $C_L = 30 \text{pF}, 3.58 \text{MHz ext.}$        |

| 8  | A        | Fall Time                     | t <sub>HLCO</sub>   |        | 100               |        | ns        | clock to OSC1                                     |

| 9  | L        | Duty Cycle                    | $DC_{CO}$           |        | 50                |        | %         |                                                   |

| 10 | I        | Capacitive Load               | $C_{LCO}$           |        |                   | 30     | pF        |                                                   |

| 11 | /        | Clock Output (CK32)           | F <sub>C32</sub>    | 32508  | 32541             | 32574  | Hz        | fc = 3.5795MHz                                    |

| 12 | O        | Rise Time                     | t <sub>LH32</sub>   |        | 100               |        | ns        | 10% - 90% of (V <sub>DD</sub> - V <sub>SS</sub> ) |

| 13 |          | Fall Time                     | t <sub>HL32</sub>   |        | 100               |        | ns        | $C_L = 100pF$                                     |

| 14 |          | Duty Cycle                    | DC <sub>32</sub>    |        | 50                |        | %         |                                                   |

| 15 |          | Capacitive Load               | C <sub>L32</sub>    |        |                   | 100    | pF        |                                                   |

| 16 |          | Warbler Frequency (TCO)       | $f_{\mathbf{W}}$    | 7.935  | 7.945             | 7.955  | Hz        | $fc = 3.5795MHz \pm 0.1\%$                        |

| 17 | <b>T</b> | Low Tone Frequency            | $f_{LT}$            | 352    | 390               | 428    | Hz        | $FATC = 0, f_c = 3.5795MHz$                       |

| 18 | T<br>O   |                               |                     | 1036   | 1148              | 1260   | Hz        | $FATC = V_{DD}, f_c = 3.5795MHz$                  |

| 19 | N        | High Tone Frequency           | $f_{HT}$            | 440    | 487               | 535    | Hz        | $FATC = 0, f_c = 3.5795MHz$                       |

| 20 | E        |                               |                     | 1295   | 1434              | 1574   | Hz        | FATC = $V_{DD}$ , $f_c = 3.5795MHz$               |

| 21 | С        | Harmonic Relationship         | $f_{HT}/f_{LT}$     |        | 1.25              |        |           |                                                   |

| 22 | A        | Warbler Output (TCO)          |                     |        |                   |        |           |                                                   |

| 23 | L        | Rise Time                     | t <sub>LHWO</sub>   |        | 500               |        | ns        | $100$ K $\Omega$ load to $V_{Ref}$                |

| 24 | L        | Fall Time                     | t <sub>HLWO</sub>   |        | 500               |        | ns        | $C_L = 30pF, MTC = 0$                             |

| 25 | E<br>R   | Duty Cycle                    | $DC_{WO}$           |        | 50                |        | %         |                                                   |

| 26 | K        | Output Level (TCO)            | V <sub>TCC</sub>    |        | $V_{\mathrm{DD}}$ |        | $V_{pp}$  | MTC = 0                                           |

| 27 |          |                               |                     |        | 0.625             |        | $V_{pp}$  | $MTC = 1$ (100KΩ load to $V_{Ref}$ )              |

| 28 | M        | Modulated Frequency           | $f_{MOD}$           |        | 32541             |        | Hz        |                                                   |

| 29 | O        | Output Level (TxO)            | $V_{TxO}$           | 225    | 250               | 270    | $mV_{pp}$ | $V_{DD} = 5V$                                     |

| 30 | D        | Output Level (TxO)            |                     |        |                   |        | •         |                                                   |

| 31 | U        | variation vs. V <sub>DD</sub> | V <sub>TxO</sub>    |        | 100               |        | %         |                                                   |

| 32 | L<br>A   | Transmit Data Input (TxDI)    |                     |        |                   |        |           |                                                   |

| 33 | T        | Rise Time                     | t <sub>LHTxDI</sub> |        |                   | 100    | ns        |                                                   |

| 34 | O        | Fall Time                     | t <sub>HLTxDI</sub> |        |                   | 100    | ns        |                                                   |

| 35 | R        | Data Rate (TxDI)              | f <sub>Data</sub>   |        | 2                 |        | k/bits    | See Note 1                                        |

## **A.C. Characteristics -** $V_{DD}$ =5.0 $V\pm5\%$ $V_{SS}$ =0V T=0 - 85 $^{\circ}$ C (All voltages are referenced to $V_{SS}$ /GND)

|    |        | Characteristics                  | Sym.             | Min. | Тур. | Max. | Unit             | Test Conditions                                   |

|----|--------|----------------------------------|------------------|------|------|------|------------------|---------------------------------------------------|

| 36 | D      | Input Impedance (RxI)            | Z <sub>IN</sub>  |      | 50   |      | ΚΩ               | 32 kHz Input Frequency                            |

| 37 | E<br>M | Valid Input Level - Data (RxI)   | V <sub>RxI</sub> | 40   |      | 400  | mV <sub>pp</sub> | See Note 2                                        |

| 38 | O      | Valid Input Level - Data + Voice | $V_{RxI}$        |      |      | 3.0  | V <sub>pp</sub>  |                                                   |

| 39 | D      | Receive Data Output (RxDO)       | $f_{Data}$       |      | 2    |      | kbit/s           |                                                   |

| 40 | L      | Rise Time                        |                  |      | 100  |      | ns               | 10% - 90% of (V <sub>DD</sub> - V <sub>SS</sub> ) |

| 41 | A<br>T | Fall Time                        |                  |      | 100  |      | ns               | $C_L = 100pF$                                     |

| 42 | Ò      | Capacitive Load                  |                  |      |      | 100  | pF               |                                                   |

| 43 | R      | Duty Cycle                       |                  | 40   | 50   | 60   | %                |                                                   |

| 44 | D      | Inband Noise Rejection (S/N)     |                  | 12   |      |      | dB               | Input Sig. $(RxI) = 400 \text{mV}_{pp}$           |

| 45 | E<br>M | Attenuation to Voice Signals     |                  | 40   |      |      | dB               | $f_{in} = 0 - 5KHz$                               |

| 46 | O      | Detect Filter Q                  | Q                |      | 3.8  |      |                  |                                                   |

| 47 | D      | Detector Center Frequency        |                  |      | 32   |      | kHz              |                                                   |

Notes: 1. All A.C. parameters are based on a typical data rate of 2 kbit/s.

2. Measured with no external resistor to DET input. Detection level internally set to 2.36 V typical.

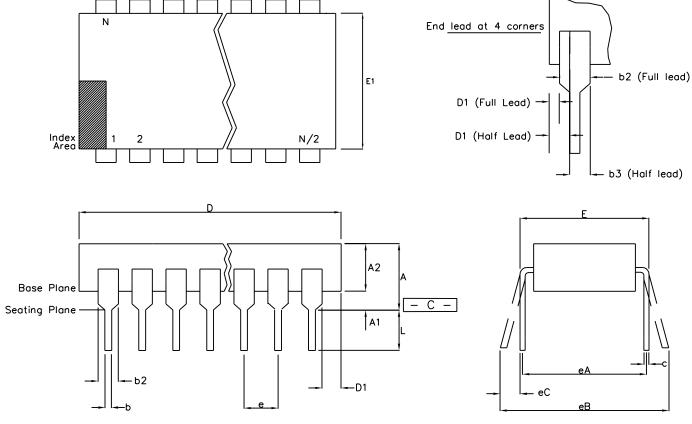

|                                    | Min Marri Min Marri |           |               |       |  |  |  |  |

|------------------------------------|---------------------|-----------|---------------|-------|--|--|--|--|

|                                    | Min                 | Max       | Min           | Max   |  |  |  |  |

|                                    | <u> </u>            | <u>mm</u> | <u>Inches</u> |       |  |  |  |  |

| А                                  |                     | 5.33      |               | 0.210 |  |  |  |  |

| A1                                 | 0.38                |           | 0.015         |       |  |  |  |  |

| Α2                                 | 2.92                | 4.95      | 0.115         | 0.195 |  |  |  |  |

| b                                  | 0.36                | 0.56      | 0.014         | 0.022 |  |  |  |  |

| b2                                 | 1.14                | 1.78      | 0.045         | 0.070 |  |  |  |  |

| b3                                 | n/a                 | n/a       | n/a           | n/a   |  |  |  |  |

| С                                  | 0.20                | 0.36      | 0.008         | 0.014 |  |  |  |  |

| D                                  | 22.35               | 23.37     | 0.880         | 0.920 |  |  |  |  |

| D1                                 | 0.13                |           | 0.005         |       |  |  |  |  |

| Е                                  | 7.62                | 8.26      | 0.300         | 0.325 |  |  |  |  |

| E1                                 | 6.10                | 7.11      | 0.240         | 0.280 |  |  |  |  |

| е                                  | 2.54                | BSC       | 0.100         | BSC   |  |  |  |  |

| eА                                 | 7.62                | BSC       | 0.300         | ) BSC |  |  |  |  |

| eВ                                 |                     | 10.92     |               | 0.430 |  |  |  |  |

| еC                                 | 0.00                | 1.52      | 0.000         | 0.060 |  |  |  |  |

| L                                  | 2.92                | 3.81      | 0.115         | 0.150 |  |  |  |  |

| N                                  | 1                   | 8         | 18            |       |  |  |  |  |

| Conforms to Jedec MS-001AC Issue D |                     |           |               |       |  |  |  |  |

#### Notes:

- 1. Leadframe Material: Copper

2. Leadframe finish: Solder Plate

3. Dimensions D, D1 & E1 do not include mould flash or protrusions.

4. Dimensions E & eA are measured with leads constrained to be perpendicular to datum C —

5. Dimensions eB & eC are measured with the leads unconstrained

6. Controlling dimensions are Inches. Millimeter conversions are not necessarily exact.

7. N is the maximum of terminal positions.

This drawing supersedes: -

Plymouth/Swindon drawing # 418/ED/39502/004

| © Zarlink | Semiconducto | r 2002 All right | s reserved. |                       |                        | Package Code        |

|-----------|--------------|------------------|-------------|-----------------------|------------------------|---------------------|

| ISSUE     | 1            | 2                |             |                       | Previous package codes | Package Outline for |

| ACN       | 202563       | 212483           |             | ZARLINK SEMICONDUCTOR | DP / E                 | 18 Lead PDIP        |

| DATE      | 9Jun97       | 5Apr02           |             | 3EMICONDUCTOR         | ·                      |                     |

| APPRD.    |              |                  |             |                       |                        | GPD00348            |

# For more information about all Zarlink products visit our Web Site at www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in and I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE